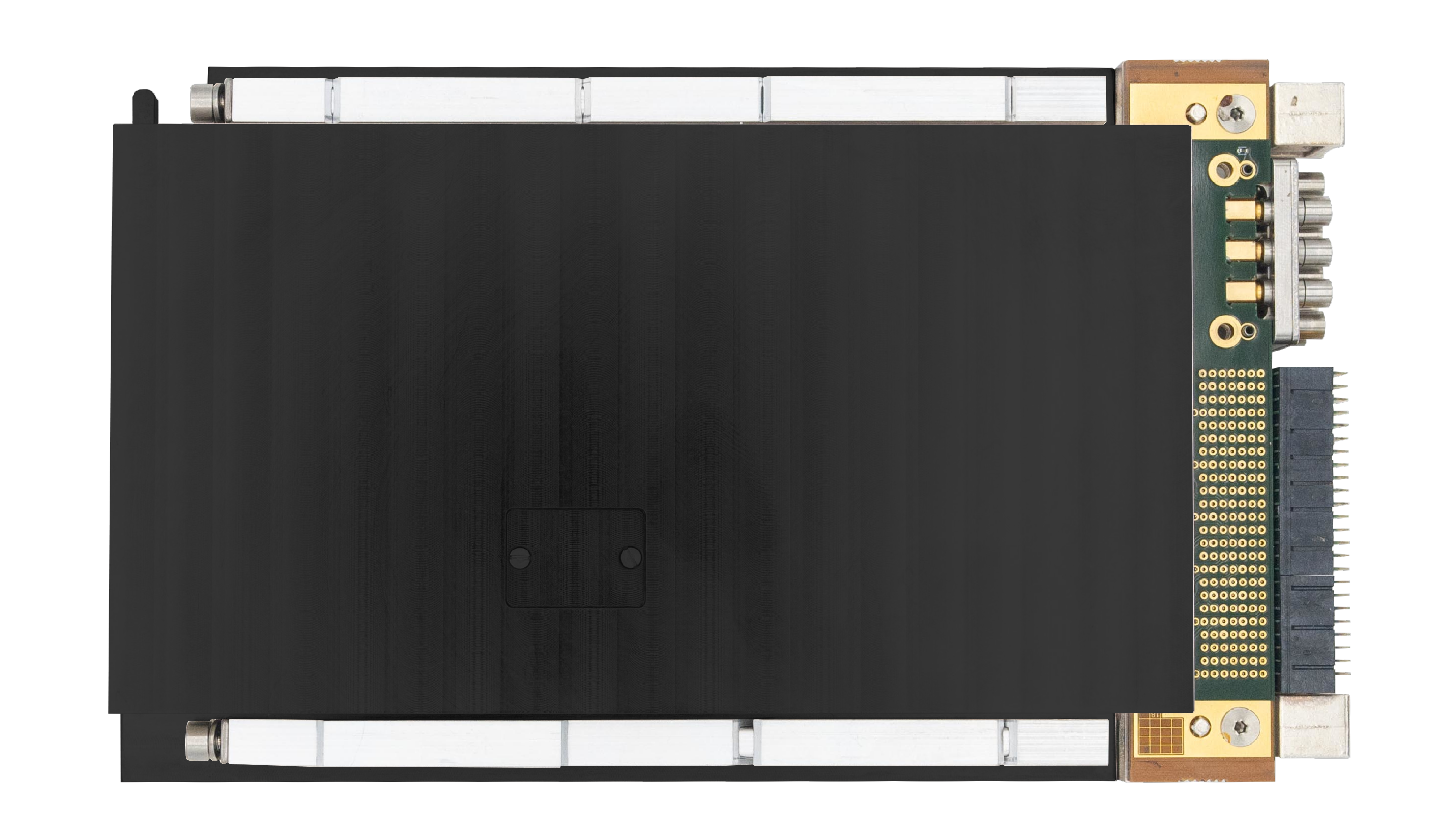

AV153, SOSA™-aligned

Presentation of the AV153, a SOSA aligned VPX board, for ultra wideband applications

Product overview

The AV153 is part of apissys’ range of Ultra Wideband Radar / ECM / SIGINT solutions based on the VITA47 ECC3, VPX standard.

This 3U VPX board combines 8x 10-bit ADCs up to 64 Gsps, 8x 10-bit DACs up to 64 Gsps, and an analog bandwidth up to 20 GHz, offering outstanding performance for demanding applications.

Fully aligned with the SOSA standard, the AV153 supports a variety of communication protocols, including PCIe, Gigabit Ethernet and a large number of user-defined I/O.

By adopting the SOSA standard, components of electronic warfare and radar systems achieve better interoperability, allowing for smoother integration and improved collaboration between elements.

The board also integrates an Altera® Agilex® 9 SoC FPGA with Direct-RF, providing high-performance processing capabilities coupled with direct radio frequency (RF) functionality, enabling seamless integration of FPGA-based processing and RF operations.

Target markets of this AV153 VPX board include Phased-Array Radar Transmitter / Receiver, Electronic Warfare ESM /ECM and Broadband Communication.

Benefits & features

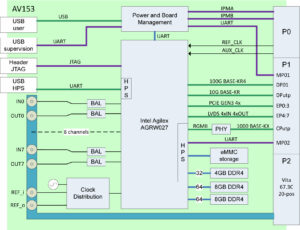

- Direct-RF SOC Intel® Agilex® 9 AGRW027

- 8 channels 64 Gsps 10-bit ADC

- 8 channels 64 Gsps 10-bit DAC

- Analog bandwidth up to 20 GHz

- Two Ultra Low jitter clock synthesizers

- External or internal sampling clock reference

- 2x 64-bit 8GBytes DDR4 2400 SDRAM (Fabric)

- 1x 32-bit 4GBytes DDR4 2666 SDRAM (HPS)

- Conduction Cooled

- SOSA-aligned

SOSA standard to improve interoperability between modules

The AV153 VPX board, which alignes with SOSA (Sensor Open Systems Architecture) standards, represents a significant advance in embedded systems for military and aerospace applications. As an essential component of the modular architecture, this board offers unrivalled flexibility and interoperability. By aligning its design with SOSA principles, it guarantees easy integration within complex systems, while facilitating component reuse and reducing development costs. Featuring 18 standardized connectors and SOSA-aligned functionalities, this VPX board offers a robust, scalable platform for the design of next-generation embedded systems, responding to the changing needs of military and aerospace missions.

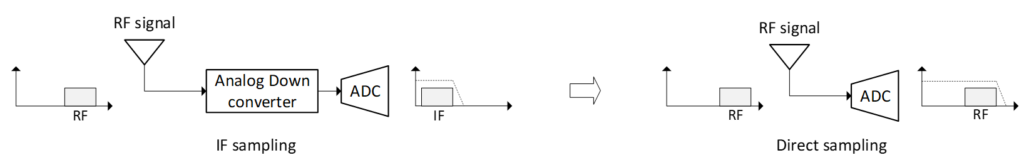

RF Direct Sampling for enhanced performance and scalability

Recent advancements in data converter technologies have significantly increased sampling rates, enabling the potential achievement of bandwidths up to several tens of gigahertz for the latest ADCs and DACs. This progress has paved the way for applications involving RF digitization, employing the intermediate frequency (IF) sampling technique.

Here, the analog signal undergoes conversion to a lower intermediate frequency before being sampled by a converter. With the rise in sampling rates, direct sampling of RF signals without additional RF conversion stages has become feasible, even for signals in the tens of gigahertz range.

Referred to as direct sampling, this approach is now applicable across various radar and EW frequency bands, including the Ku, K, and Ka bands. Implementing the RF direct sampling method can streamline architectures and improve equipment flexibility, scalability, and SWAP-C (Size, Weight, Power, and Cost).

apissys, an expert in wideband conversion solutions, is dedicated to designing products leveraging cutting-edge technology to offer direct sampling capabilities for radar and electronic warfare applications.

Tech specs

Form Factor

- 3U VPX Conduction cooled Vita 48.2, pitch 1.0”

VPX Profile

- SLT3-PAY-1F1U1S1S1U1U2F1H-14.6.11-12

Analog Input/Output

- Input coupling: AC

- Full power bandwidth: 100MHz to 20 GHz

- Full scale: TBD

- Output coupling: AC

- Full power bandwidth: 100MHz to 20 GHz

- Full scale: TBD

- Impedance: 50 Ohm

- Connectors: Vita 67.3 NanoRF

Analog-Digital Conversion

- Eight channels, up to 64Gsps

- Resolution: 10 bit

- Sampling Performances at 64Gsps

- NSD: -150 dBFS/Hz at -3dBFS at 6GHz

- SDFR: -56.19 dBc at -3dBFS at 6GHz

Digital-Analog Conversion

- Eight channels, up to 64Gsps

- Resolution: 10 bits

- Sampling Performances at 64Gsps

- NSD: -156 dBFS/Hz at 0dBFS at 6GHz

- SDFR: -51 dBc at 0dBFS at 6GHz

Clock

- Two Ultra-low jitter clock synthesizers

- External or internal sampling clock reference

- Impedance: 50 Ohm

- Connectors: Vita 67.3 NanoRF

Memory

- Two banks 64-bit 4GBytes DDR4 2400 SDRAM (fabric)

- One bank 64-bit 4GBytes DDR4 2400 SDRAM (HPS)

- One 2 Gbit QSPI FLASH memory

- eMMC storage (HPS)

Operating Temperature

- ECC3, -40°C to 70°C

VPX interface

- P1:

- Data plane: one fat pipe DP01 supporting 100GBASE-KR4

- Data plane: one ultra-thin pipe DPutp01 supporting 10GBASE-KR

- Control plane: one ultra-thin pipe CPutp01 supporting 1000BASE-KX

- Expansion plane: one fat-pipe supporting PCIE GEN3 4x

- Expansion plane: 8 LVDS differential pairs

- P2:

- Vita 67.3C Aperture H

- NanoRF Contacts-6.4.5.6.10

- 8xIN, 8xOUT, REFIN, REFOUT

Power dissipation

- +12V: 14 A max (170W) TBD

- +3.3VAUX: 0.6A max (2W) TBD

Weight

- 630g TBD

Board Support Package

- FPGA + HPS exemple design

- SW API and examples, Windows 10 64-bits / Linux 64-bits

- User manuals

- Quick start guide

Deliverables

Board Support Package

- FPGA example design

- Communication

- Front-Panel USB to Avalon

- JTAG to Avalon

- Data Conversion

- Clock component access

- 64Gsps support

- 8x ADC, Decimation x16 support

- 8x DAC, Interpolation x16 support

- ADC acquisition buffers

- DAC generation buffers

- Memory

- DDR4 Avalon access

- System management

- Avalon access to monitoring

- infrastructure

- Communication

- HPS example design

- Linux distribution built on Yokto

- HPS Interfaces:

- eMMC 128Gb

- RGMII GbE

- UART

- EMIF (Memory interface)

- 4GB DDR4 Memory

- Services

- SSH server only

- No direct access to FPGA

- SW API and examples, Windows 10 64-bits / Linux 64-bits

- User manuals

- Quick start guide